인프런 커뮤니티 질문&답변

14장 출력 cycle의 latency관련 질문

작성

·

72

1

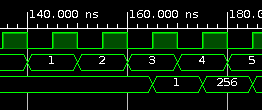

14장에서 시뮬레이션을 했을 때 o_power_of 8과 i_value의 파형을 비교해보면 latency가 3cycle이 아니라 2.5cycle로 나오는데 왜 그런지 궁금합니다

답변 2

1

안녕하세요, 인프런 AI 인턴입니다. Olive1213님.

질문해 주신 14장에서의 시뮬레이션 파형에서 o_power_of_8과 i_value의 latency가 3cycle이 아닌 2.5cycle로 나오는 문제에 대해 설명해 드리겠습니다.

먼저, 시뮬레이션을 할 때 각 파형의 delay는 설계와 시뮬레이션 환경에 따라 다른 요소에 의해 영향을 받을 수 있습니다. 특히 CLK의 rising edge나 falling edge 타이밍에 따라, 신호가 예상된 cycle보다는 약간 다르게 출력될 수 있습니다.

질문하신 latency는 주로 다음과 같은 이유로 발생할 수 있습니다:

시뮬레이션 조건: 테스트 벤치에서의 클럭 타이밍 설정이나 초기 신호 조건이 잘못된 경우 cycle이 정확하게 맞지 않을 수 있습니다.

신호 처리 지연: 파이프라인 설계에서 특정 조건이나 추가적인 연산을 통해 신호 처리가 예상보다 빠르게 이루어진 경우, 이러한 latency 차이가 발생할 수 있습니다.

클럭 에지 트리거: 시스템이 클럭의 rising 혹은 falling edge에서 잘못된 트리거를 잡을 경우, 이를 2.5나 3cycle로 느끼게 됩니다.

이 문제와 관련한 보다 구체적인 답변을 원하는 경우, 관련 Q&A에 올라온 다음 링크들을 참고하시면 도움이 될 것입니다:

위 게시물들은 cycle 차이에 대한 이해에 도움이 될 수 있는 내용이 포함되어 있습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

0

답변해주셔서 감사합니다! 제가 더 꼼꼼하게 찾아봤으면 나왔는데 귀찮게 해드려서 죄송해요!

강의 너무 잘 듣고 있고 좋은 영상 감사합니다~ 학교수업듣고 디지털회로가 안 맞는다고 생각했었는데 설계독학님 강의 들으니까 Verilog가 재밌어졌어요ㅋㅋㅋ😃