인프런 커뮤니티 질문&답변

MOR에 사용하는 FIFO에 대한 질문 드립니다.

작성

·

115

1

맛비님. 안녕하세요.

좋은 강의 항상 잘 보고 있습니다.

MOR에 대해 질문이 있습니다.

RDMA에서 FIFO의 data에 burst len을 입력하는 것으로 해석됩니다. 만약 이런 경우라면

0x20000000번지에서 128 바이트를 읽는 중

0x2000C000번지에 128 바이트를 읽는 식으로 동작이 되나요?

제가 코드를 봤을 땐 위처럼 동작이 불가능해보여서요.

만약 제가 생각한게 맞고 위처럼 동작하도록 수정하려면 메모리 주소 FIFO와 burst len FIFO 두 개를 사용해야할까요?

================ 다음 내용은 읽어보시고 지우시면 됩니다.=================

질문 내용을 작성해주실 때, 위의 3단계로 제가 이해할 수 있게 작성해주시면 정확한 답변을 드릴 수 있을 것 같아요!!

현업자인지라 업무때문에 답변이 늦을 수 있습니다. (길어도 만 3일 안에는 꼭 답변드리려고 노력중입니다 ㅠㅠ)

강의에서 다룬 내용들의 질문들을 부탁드립니다!! (설치과정, 강의내용을 듣고 이해가 안되었던 부분들, 강의의 오류 등등)

이런 질문은 부담스러워요.. (답변거부해도 양해 부탁드려요)

개인 과제, 강의에서 다루지 않은 내용들의 궁금증 해소, 영상과 다른 접근방법 후 디버깅 요청, 고민 상담 등..

글쓰기 에티튜드를 지켜주세요 (저 포함, 다른 수강생 분들이 함께보는 공간입니다.)

서로 예의를 지키며 존중하는 문화를 만들어가요.

질문글을 보고 내용을 이해할 수 있도록 남겨주시면 답변에 큰 도움이 될 것 같아요. (상세히 작성하면 더 좋아요! )

먼저 유사한 질문이 있었는지 검색해보세요.

잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

==================

답변 3

1

답변 감사합니다.

코드에서는 FIFO에 ARLEN만 넣어줘서 의문이 생겼는데 이제야 좀 이해가 가는거 같아요.

메모리도 AXI4 I/F를 사용하기 때문에 MOR 지원이 되니까 AR hand shake가 발생하면 FIFO에 다음 읽어올 burst len만 넣어주는 거 같네요. 맞을까요?

근데 추가로 궁금한 점이 생기는데요. 같은 질문이긴 하지만 컨트롤러를 통해 DMA 설정을 만약

0x20000000번지에서 128 byte read (1)

0x2000c000번지에서 128 byte read (2)

이것도 MOR이 될까요?

(1)의 작업이 실행 중이라면 Module FSM의 상태가 S_RUN일텐데 이 때 (2) 작업에 대한 DMA 설정이 r_real_base_addr과 r_num_total_stream_hs가 사용자가 입력한 값으로 업데이트가 되지 않을 것 같아서요.

matbi_rdma.v, code line 272-280, code line 326-334에 코드를 참고했습니다.

0

안녕하세요 🙂

AXI4 의 Read 에는 두개의 channel 이 존재합니다.

R Addr, R Data.

각 channel 은 독립적으로 수행할 수 있도록 설계되어 있습니다.

즉 R Addr, R Data 채널은 Pipeline 관계에 놓입니다.

전달드린 예제에서 R Data 는 "in order" 입니다.

"in order" 의 의미는 read req 를 발행한 순서대로 r data 가 들어온다는 뜻입니다.

================

RDMA에서 FIFO의 data에 burst len을 입력하는 것으로 해석됩니다. 만약 이런 경우라면

0x20000000번지에서 128 바이트를 읽는 중

0x2000C000번지에 128 바이트를 읽는 식으로 동작이 되나요?

질문에서 모호한 부분이 있어 보이는데요. R Req, R data 를 따로 분리해서 질문을 주셔야 옳은 것 같아요. 그렇다고 가정해보면,

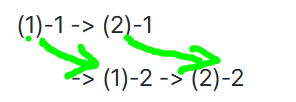

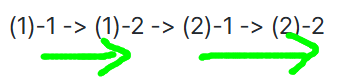

Address 0x20000000번지 읽음, (1)

R Addr : 0x20000000번지 R req "(1)-1 로 정의"

R Data : 0x20000000번지 R Data "(1)-2 로 정의"

Address 0x2000C000 번지 읽음, (2)

R Addr : 0x2000C000번지 R req "(2)-1 로 정의"

R Data : 0x2000C000번지 R Data "(2)-1 로 정의"

각 channel 은 독립적으로 수행할 수 있도록 설계되어 있으니 timeline 은 다음과 같습니다.

만약 순차 Req, Data 라면. (현재 강의이 AXI4-Lite 시뮬레이션 처럼) 다음과 같은 time line 을 갖겠죠.

즐공하세요 🙂

0

안녕하세요, 인프런 AI 인턴입니다. 김상현님!

RDMA 설계에서 MOR에 사용하는 FIFO에 대해 궁금하신 점을 올려주셨네요. RDMA에서 서로 다른 메모리 주소로의 연속적인 read 요청을 처리하는 데 있어서, 데이터와 관련된 주소, burst length 등을 어떻게 관리하는지가 핵심인 것 같습니다.

FIFO를 사용하여 머리 주소와 burst 길이를 관리하는 방식에 대한 설명이 필요할 수 있습니다. 일반적으로 이러한 시스템에서 메모리 주소와 burst 길이는 각각 독립적인 FIFO로 관리되기도 하는데요, 이는 여러 독립적인 read 요청을 효과적으로 큐잉하고 처리하기 위해서입니다.

FIFO의 데이터 구조를 통해 0x20000000 번지에서 128 바이트를 읽은 후, 곧바로 0x2000C000 번지에서 128 바이트를 읽는 방식으로 처리할 수 있는지 질문하셨는데요, 이는 FIFO가 각 요청당 관련된 주소와 길이를 올바르게 관리할 수 있는 경우에 가능할 것입니다.

관련 질문들이 다뤄진 예시를 참고해 보시면 도움이 될 수 있습니다:

- rdma 설계시 FIFO payload에 대한 의문 +@: RDMA 설계 시에 FIFO의 적절한 사용법과, 설계에서 고려해야 할 부분들을 설명합니다.

이해를 돕기 위해 질문자의 상황과 유사한 내용을 포함한 자료나 강의 내용을 복습해보시는 것도 좋은 방법입니다. 이를 통해 FIFO 사용과 주소 관리 방식을 더 잘 이해할 수 있을 것입니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다. 현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏 추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

네 이해하신게 맞는 것 같아요.

AR channel 과 R channel 이 분리 되어 있어서,

Slave 가 AR channel 의 (1) 이후 바로 (2) 를 받아줄 수 있는 환경이라면, 이어서 Request 가 가능합니다. 저희는 FIFO 의 depth 만큼의 개수 만큼 연속으로 줄 수 있겠네요.

즐공하세요 🙂