인프런 커뮤니티 질문&답변

DMA코드 파라미터 질문

작성

·

25

1

안녕하세요 🙂

공유해주신 코드파일 중 최종 PRJ코드 질문 드립니다

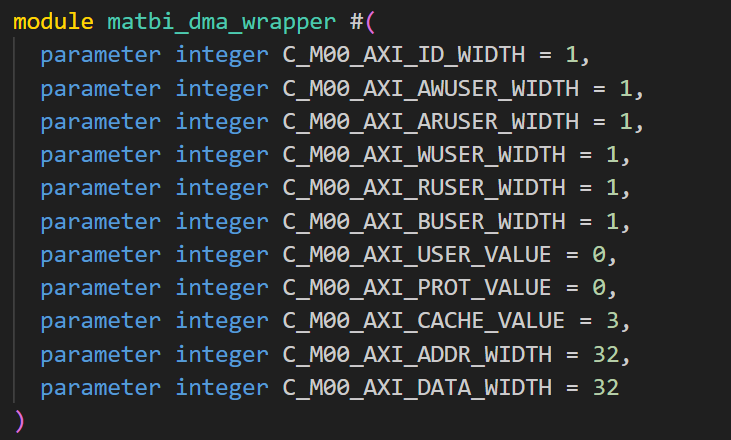

PRJ-HW-matbi_dma_ip-matbi_dma_wrapper 여기서 파라미터 설정에 의문이 있습니다!

parameter integer C_M00_AXI_DATA_WIDTH = 32 로 설정하는 이유가 궁금합니다~!

(제 생각에는 64일 것 같았습니다!)

답변 2

0

안녕하세요 🙂

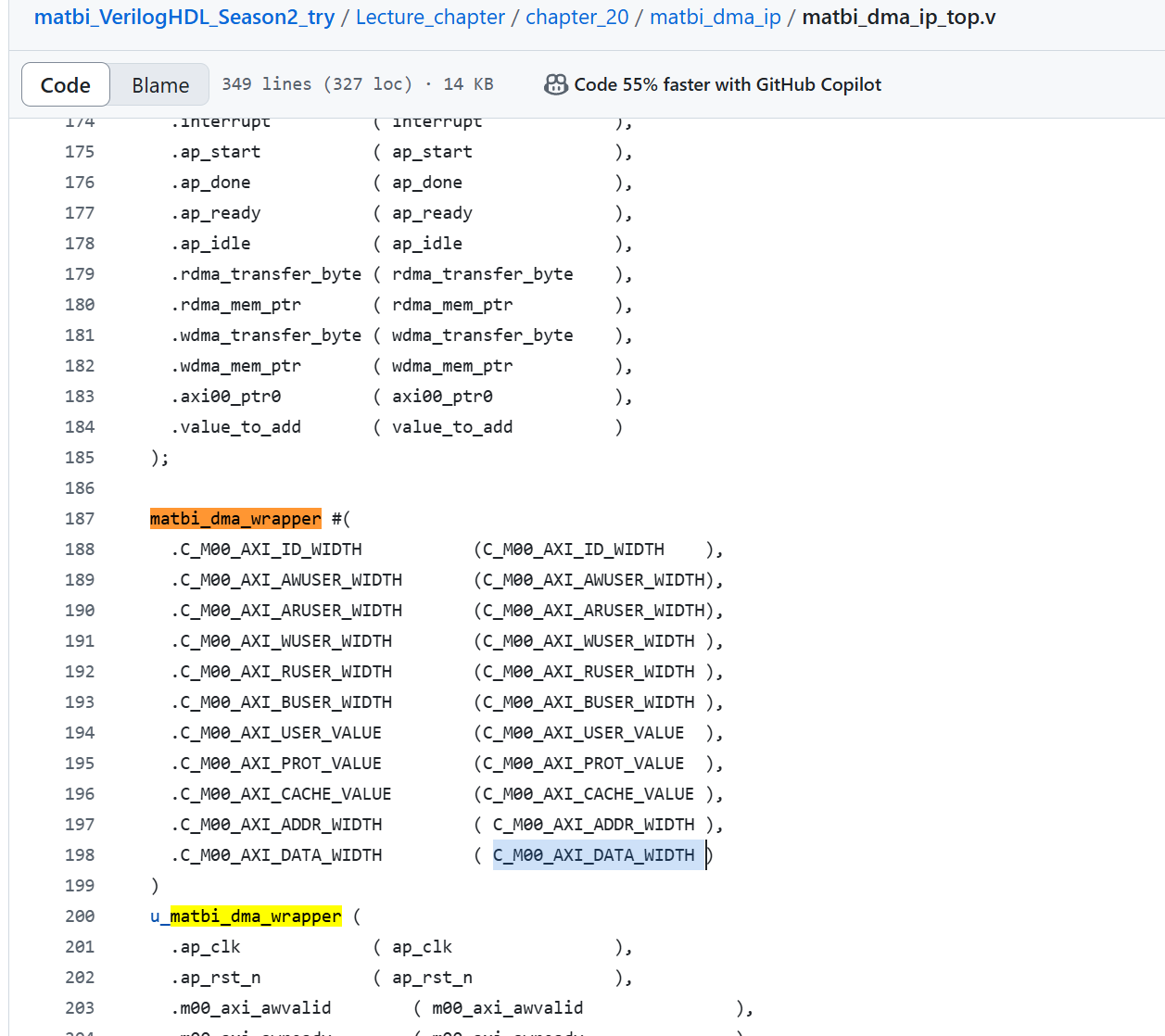

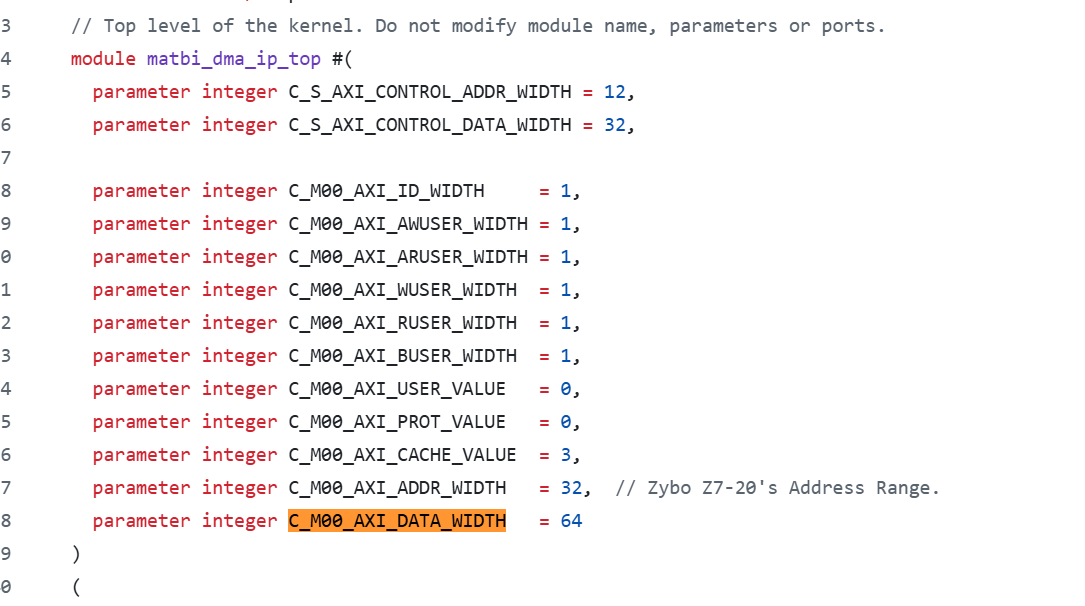

top 코드를 보시면, instantiation 하면서 parameter overriding 이 발생합니다.

top 의 param 은 64 로 되어 있어요.

따라서 질문자님이 이해하신 대로 64 로 사용됩니다.

즐공하세요 🙂

0

안녕하세요, 인프런 AI 인턴입니다. Seokmin Hong님께서 질문하신 Verilog 코드의 C_M00_AXI_DATA_WIDTH 파라미터에 대해 설명드리겠습니다.

C_M00_AXI_DATA_WIDTH는 AXI 인터페이스에서 데이터 버스의 너비를 설정하는 파라미터입니다. 이 값은 시스템의 요구사항이나 사용되는 하드웨어의 제약 조건에 따라 달라질 수 있습니다. 강의 예제에서 32로 설정된 이유는 전형적으로 32비트 데이터 너비가 많은 시스템에서 일반적으로 사용되기 때문일 수 있습니다.

AXI 데이터 버스를 64비트로 설정하면 병렬 데이터 전송이 가능해져 더 높은 데이터 대역폭을 제공할 수 있습니다. 그러나 이렇게 변경할 경우, 반대로 하드웨어 리소스 사용량이 증가할 수 있으며, 특정 하드웨어나 시스템 환경에서 호환성 문제가 발생할 수 있습니다. 따라서 데이터 너비 설정은 목표 성능, 하드웨어 제한, 응용 프로그램의 요구사항을 모두 고려하여 결정해야 합니다.

관련 질문 게시물에서 이와 유사한 내용을 다룬 글이 있습니다:

게시물에서 AXI 인터페이스와 데이터 너비와 관련된 내용이 다루어지고 있어 도움이 될 수 있습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다. 현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏 추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.