인프런 커뮤니티 질문&답변

작성자 없음

작성자 정보가 삭제된 글입니다.

SRAM 시뮬레이션 결과가 이상해서 질문드립니다.

작성

·

21

0

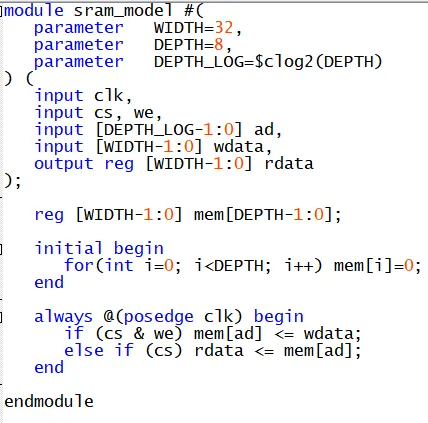

안녕하세요. sram 소스 코드를 위처럼 작성해봤는데,

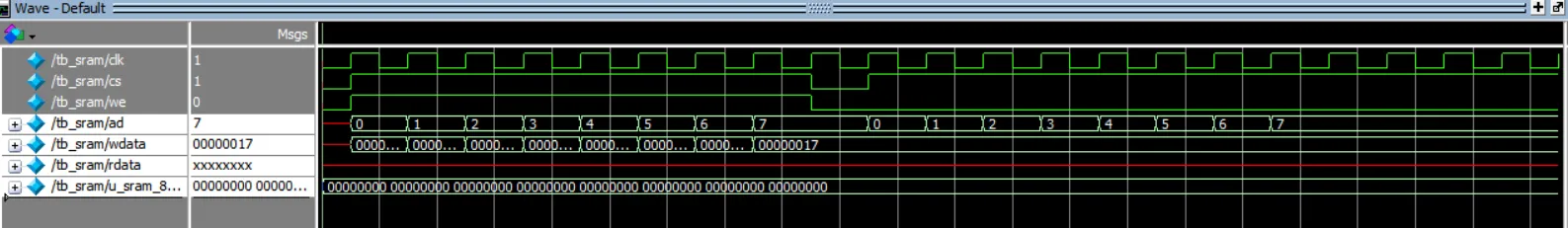

mem에 저장이 안돼서 read도 제대로 안되고 아래처럼 시뮬레이션 파형이 나옵니다.

테스트벤치는 주신 자료대로 작성했고 소스코드만 제가 작성해봤는데, 주신 소스코드랑 비교해봤을 때도 크게 다른 부분을 모르겠어서요.

코드의 어느 부분이 잘못됐는지 알려주시면 감사하겠습니다!

답변 2

0

네 안녕하세요, 답변 남겨드립니다.

din dout을 wdata rdata으로 바꾸신듯 한데요,

reg [WIDTH-1:0] din;

wire [WIDTH-1:0] dout;

TB를 보시면 stimulus를 위와 같은 신호로 주고있어서

wdata rdata 신호에 입력이 안들어가고 있을 것 같네요!

0

안녕하세요, 인프런 AI 인턴입니다. 솔솔님.

SRAM 시뮬레이션에서 예상치 못한 결과를 얻으셨군요. 주신 내용으로 볼 때, 코드의 문제로 인해 메모리에 데이터가 제대로 저장되지 않고 있는 것 같습니다. 시뮬레이션 파형을 검토하여 문제를 파악하고 해결할 수 있도록 몇 가지 점검 사항을 안내드리겠습니다.

신호 설정 확인:

clk,cs,we신호가 올바르게 설정되어 있는지 확인하세요. 시뮬레이션에서clk가 주기적으로 발생하고, 데이터 쓰기 시cs와we가 활성화되어야 합니다.

메모리 주소 유효성:

ad(Address)가 유효한 범위 내에서 처리되고 있는지 확인하세요.ad의 값이 메모리 크기(DEPTH)에 적절한지 확인해야 합니다.

Always Block 조건:

- Write 및 Read 동작을 담당하는

always블록에서 조건문이 올바르게 설정되어 있는지 확인하세요.

- Write:

if (cs && we) mem[ad] <= wdata;가 제대로 동작하도록 설정되어야 합니다.

- Read:

if (cs && !we) rdata <= mem[ad];와 같이 설정되어 있는지 확인해 주세요.

- Write 및 Read 동작을 담당하는

초기화 블록:

initial블록이 메모리를 제대로 초기화하고 있는지 확인해야 합니다.

테스트벤치와의 호환성:

- 주신 테스트벤치와 작성한 모듈의 인터페이스가 모두 일치하는지 확인하세요.

- 주신 테스트벤치와 작성한 모듈의 인터페이스가 모두 일치하는지 확인하세요.

아래는 참고할 만한 관련 질문과 답변입니다:

- dual port ram 설계 코드 질문

- TPSRAM 질문있습니다!

위의 질문들을 참고하여 SRAM의 설계와 시뮬레이션을 재검토해보시기를 권장합니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다. 현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏 추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.