인프런 커뮤니티 질문&답변

axi4 bus의 data bit width 관련

작성

·

114

1

안녕하세요

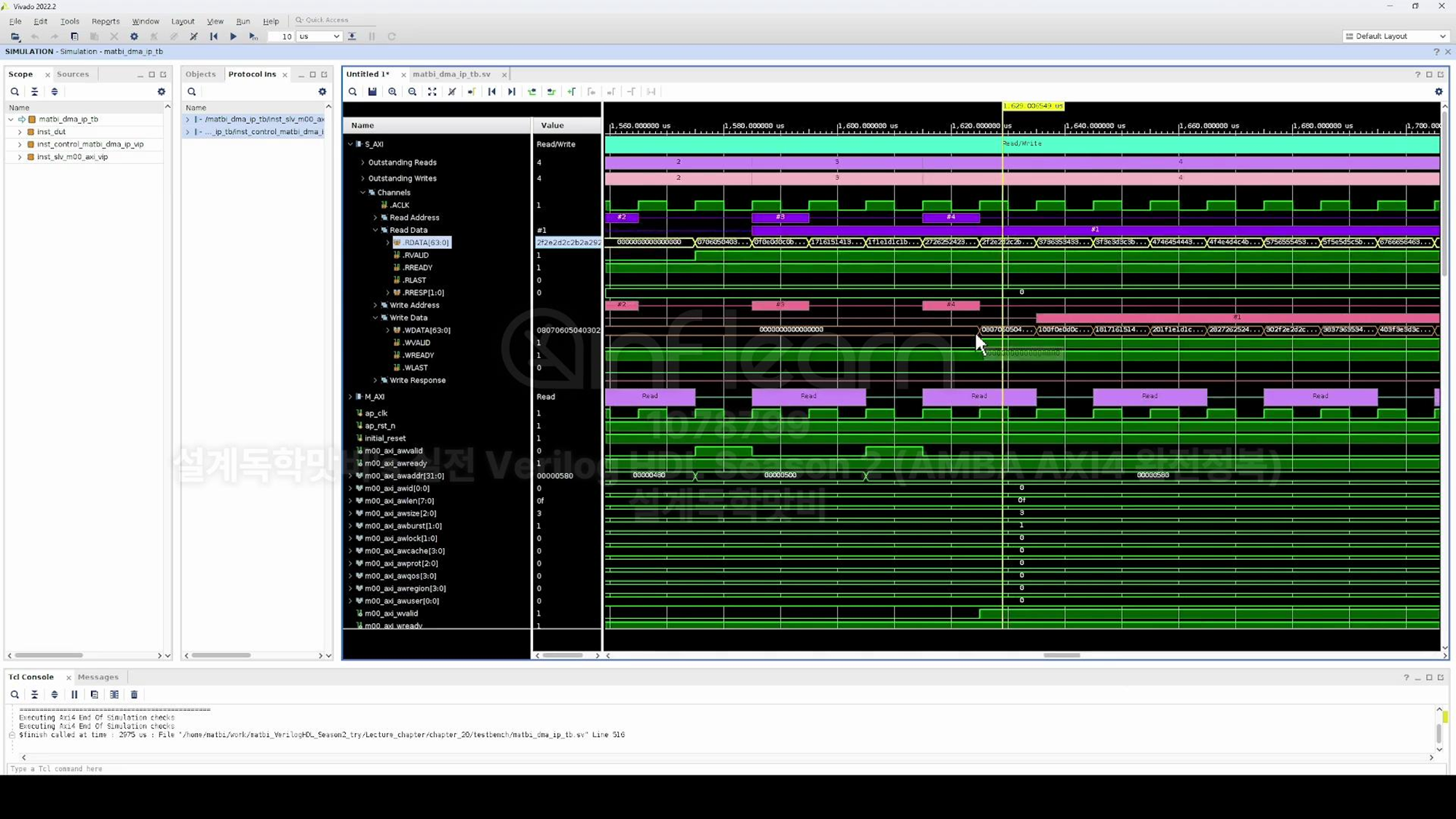

해당 캡쳐 화면에서는 Read data와 Write data가 처음 4cycle을 제외하곤 이후에 동시에 움직이고 있습니다. 그렇다면 읽는거 64b, 쓰는거 64b -> 합쳐서 128b로 AXI4 Bus Data Width를 사용하고 있다고 생각해도 되는 것일까요?

해당 캡쳐 화면에서는 Read data와 Write data가 처음 4cycle을 제외하곤 이후에 동시에 움직이고 있습니다. 그렇다면 읽는거 64b, 쓰는거 64b -> 합쳐서 128b로 AXI4 Bus Data Width를 사용하고 있다고 생각해도 되는 것일까요?

앞서 fpga 시즌1 강의에서 AXI4 lite를 사용할때는 '다 읽고' -> '다 연산' -> '다 쓰기' 이렇게 나누어서 진행했던터라 axi4 lite에 대해서도 궁금한 점이 생겼는데요! 위와 같이 read data channel(R), write data channel(W)이 동시에 일할수도 있는건가요?? 그럼 32b 데이터 2개가 bus를 동시에 쓰는 거니까 64b bus data width 인건가요??

질의응답 해주시는 노고에 정말 감사드립니다 ㅜㅜ

답변 1

1

설계독학맛비

지식공유자

안녕하세요 🙂

Read channel 과 Write channel 은 서로 독립적으로 존재하는데요.

AXI4 Bus Data Width 는 따라서 64b 으로 표현하시는게 맞습니다. (R : 64b, W : 64b 으로 말하고요. 합쳐서 128b? 이라고 표현은 잘 안하는 것 같아요)

시즌 1에서는 난이도가 쉬운 방법이라, 순차적이었어요.

원래는 현업가시면, full performance 를 위해서 동시 사용 설계가 올바른 방향이라고 생각합니다. (그만큼 어렵겠지만..?! 그래서 실력을 키워야겠죠..?!!)

즐공하세요 🙂

너무 명쾌한 답변이예요 .. 속이 뻥 뚫렸어요 감사합니다!