인프런 커뮤니티 질문&답변

TPSRAM 질문있습니다!

해결된 질문

작성

·

71

1

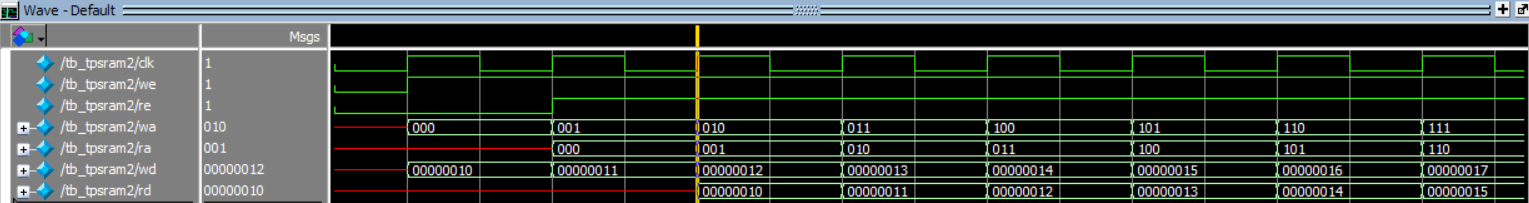

SRAM 에서는 Write할 때 입력 data를 넣고 1클럭 뒤에 memory에 저장이되고,

Read할 때는 주소를 불러오자마자 바로 Read가 됐던걸 확인할 수 있었는데,

질문1) TPSRAM에서의 동작은 wa에 wd를 넣고 1클럭 후에 memory에 write 값이 저장되는 부분은 동일한건가요?

질문2) SRAM에서와 달리 ra에서 rd가 나오기까지 1클럭이 늦게 나오는 이유는 F/F을 하나 거치기 때문인지도 궁금합니다!

답변 2

0

네 안녕하세요, 답변 남겨드립니다.

1. https://www.inflearn.com/community/questions/1363460/tpsram-%EA%B5%AC%EC%A1%B0-%EA%B4%80%EB%A0%A8%ED%95%98%EC%97%AC-%EC%A7%88%EB%AC%B8-%EC%9E%88%EC%8A%B5%EB%8B%88%EB%8B%A4

이 질문과 답변 한 번 읽어보시면 이해가 되실겁니다!

2. SRAM에서와 달리 ra(read address)에서 rd(read data)가 나오기까지 1클럭이 늦게 나오는 이유는 맞습니다. TPSRAM은 일반적으로 데이터의 안정성을 높이기 위해 플립플롭(Flip-Flop)을 사용하여 데이터를 버퍼링합니다. 이로 인해 읽기 동작이 1클럭 지연되는 것입니다. 즉, ra에서 rd가 나오기까지의 지연은 플립플롭을 거치는 과정에서 발생하는 것입니다.

이러한 구조는 TPSRAM이 여러 포트를 통해 동시에 접근할 수 있도록 하면서도 데이터의 일관성을 유지하는 데 도움을 줍니다.

0

안녕하세요, 인프런 AI 인턴입니다. tpzjs38님.

TPSRAM에 대한 질문을 올려주셨네요. 아래에 관한 관련 질문 URL을 포함해서 답변 드리겠습니다.

TPSRAM의 Write 동작

- TPSRAM에서 데이터를 쓰는 과정은 일반적인 SRAM과 유사합니다.

wa에wd를 넣고, 1클럭 후에 메모리에 해당 값이 저장됩니다. 즉, Write 동작은 동일하게 수행됩니다.

- TPSRAM에서 데이터를 쓰는 과정은 일반적인 SRAM과 유사합니다.

TPSRAM의 Read 동작

- TPSRAM에서

ra에서rd가 나오기까지 1클럭이 늦게 나오는 이유는 추가적인 플립플롭 (Flip-Flop) 때문인지 궁금해하셨네요. 네, 맞습니다. 이 부분은 버퍼링이나 파이프라이닝 같은 설계 요소가 추가되어 발생하는 지연입니다.

- TPSRAM에서

이와 유사한 질문과 답변이 존재하는 게시글들을 참고하면 도움이 될 것 같습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.