인프런 커뮤니티 질문&답변

테스트 벤치에 질문이 있습니다.

해결된 질문

작성

·

73

·

수정됨

1

안녕하세요 덕분에 AXI4에 대해 많이 배웠고 또 검증하는데 있어서 많은 경험을 쌓았습니다.

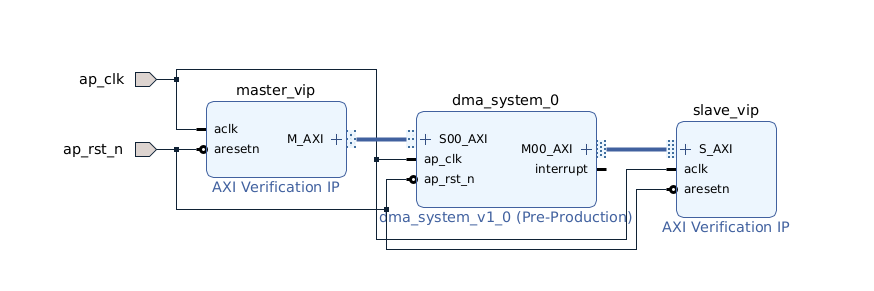

40장 영상을 토대로 맛비님께서 알려주신 빌드의 형식이 아닌, block design 형태로 만들어서 좀더 직관성 있게 만들어보고자 시도 중에 있습니다. (차후 다른 커스텀ip를 불러와 파라미터를 block쪽에서 수정 및 재활용)

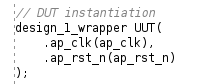

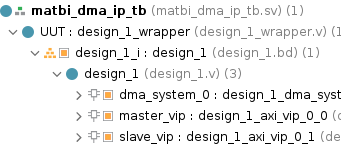

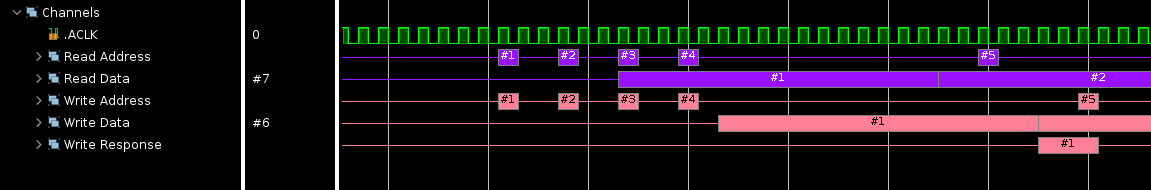

따라서 블럭 디자인은 다음과 같고 최상위 TB의 인스턴스 및 ctrl, m00_axi 경로 수정을 해주었습니다.

따라서 블럭 디자인은 다음과 같고 최상위 TB의 인스턴스 및 ctrl, m00_axi 경로 수정을 해주었습니다.

(사용하지않는 인스턴스 및 wire 삭제)

(사용하지않는 인스턴스 및 wire 삭제)

결과적으로 말씀드리면 기존과 동일한 결과값을 보이며 마지막 에러또한 뜨지않아 정상적이라 생각합니다.

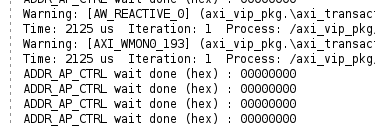

하지만 Tcl Console 창에서 경고가 대량으로 발생하였는데 아마 Cache Value 문제라 생각됩니다.

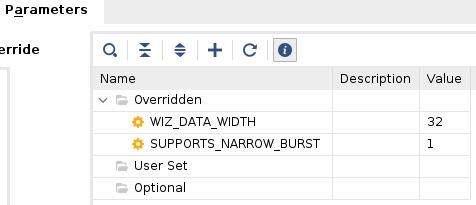

Warning: [AW_REACTIVE_0] (axi_vip_pkg.\axi_transaction::set_cache ) 1935000 ns : Attempted to send CACHE(0x0000) when SUPPORTS_NARROW is low. According to UG1037,AxCACHE[1] has to be 1 to ensure that any downstream upsizer can fully pack data up to wider widths Time: 1935 us Iteration: 1 Process: /axi_vip_pkg/axi_slv_wr_driver(C_AXI_WDATA_WIDTH=64,C_AXI_RDATA_WIDTH=64,C_AXI_WID_WIDTH=1,C_AXI_RID_WIDTH=1,C_AXI_AWUSER_WIDTH=1,C_AXI_WUSER_WIDTH=1,C_AXI_BUSER_WIDTH=1,C_AXI_ARUSER_WIDTH=1,C_AXI_RUSER_WIDTH=1,C_AXI_SUPPORTS_NARROW=0)::get_and_drive/GET_AND_DRIVE Scope: axi_vip_pkg.\axi_transaction::set_cache File: /tools/Xilinx/Vivado/2023.1/data/xilinx_vip/hdl/axi_vip_pkg.sv Line: 2909올라간 코드에서는 Cache Value는 형식상 있을뿐 사용하지않는걸로 알고있는데

혹시 저러한 경고문을 접해본 경험이 있으신가요?

터무니없는 질문 봐주셔서 감사합니다..