인프런 커뮤니티 질문&답변

dual port ram 설계 코드 질문

해결된 질문

작성

·

117

1

module dpsram #(

parameter DEPTH=8,

parameter WIDTH=32,

parameter DEPTH_LOG=$clog2(DEPTH)

)(

input clk,

input [WIDTH-1:0] din_a,

input [WIDTH-1:0] din_b,

input [DEPTH_LOG-1:0] addr_a,

input cs_a,

input we_a,

input [DEPTH_LOG-1:0] addr_b,

input cs_b,

input we_b,

output reg [WIDTH-1:0] dout_a,

output reg [WIDTH-1:0] dout_b

);

reg [WIDTH-1:0] mem[DEPTH-1:0];

initial begin

for(int i=0;i<DEPTH;i++) mem[i]=0;

end

always@(posedge clk) begin //write

if(we_a && cs_a) mem[addr_a] <= din_a;

if(we_b && cs_b) mem[addr_b] <= din_b;

end

always@(posedge clk) begin //read

if(~we_a && cs_a) dout_a <= mem[addr_a];

if(~we_b && cs_b) dout_b <= mem[addr_b];

end

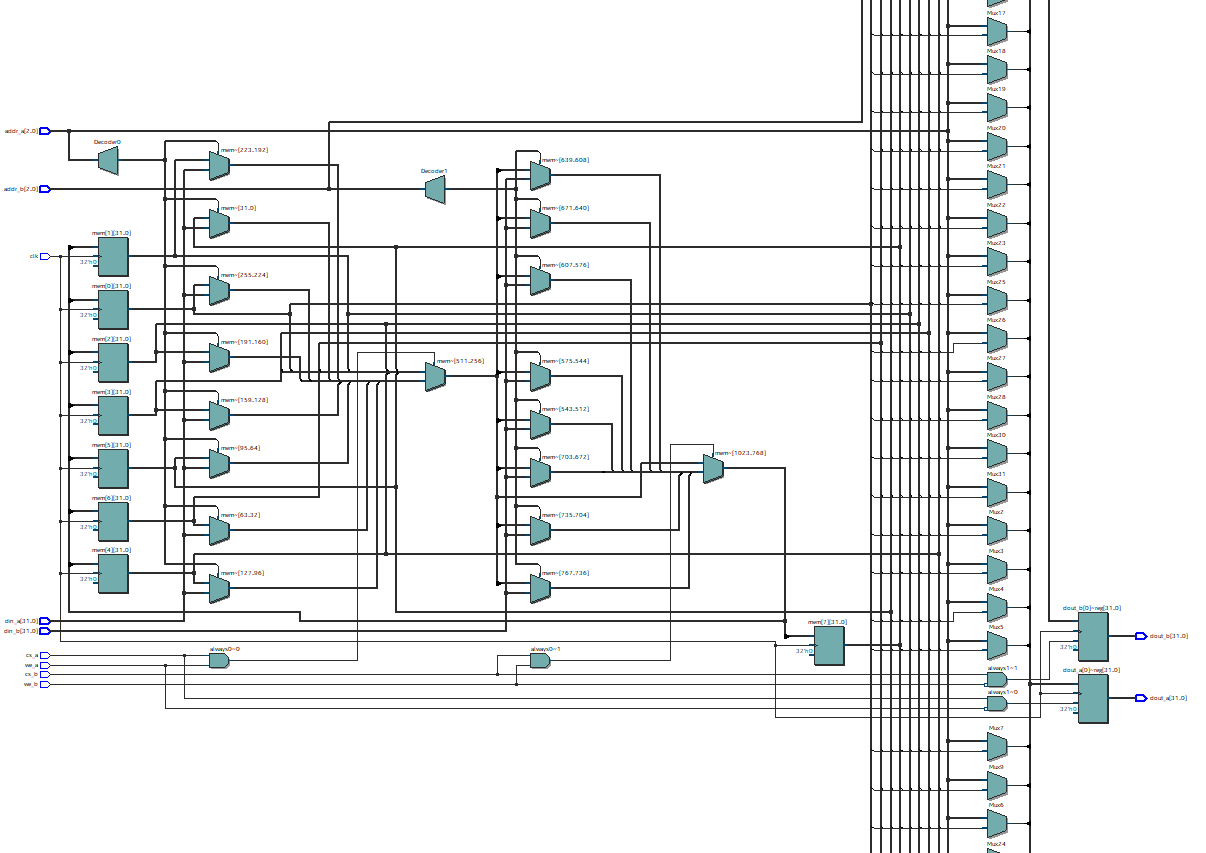

endmodule위와같이 dpsram코드를 짰습니다. 예제 코드와는 다르게 저는 write와 read를 각각 나눠서 always block을 구성했는데 이렇게 짜면 다르게 동작하나요? RTL 뷰어로 보니 아래와 같이 복잡하게 나와서 질문드립니다.

답변 1

0

회로설계 멘토 삼코치

지식공유자

네 안녕하세요, 답변 남겨드립니다.

먼저 위와 같이 작성해도 돌아갈것 같긴 한데, 좋은 코드는 아닙니다. 왜냐하면 지금은 조건문에서 서로 겹치는것이 없어서 괜찮지만 혹시라도 if 조건문이 겹치게 되면 신호가 blocking 될 수도 있을듯 합니다.

한 번 시뮬레이션 테스트벤치를 똑같이 돌려보고 결과 비교해보시겠어요? 잘 돌아갈 것 같긴 합니다.

또한 합성 결과가 다른 이유는, Quartus는 메모리의 형태가 갖추어진 코드의 경우, 자체적으로 내장되어있는 메모리를 사용하게 됩니다. 따라서 저의 예시 코드는 일반적 메모리의 형태를 갖추고 있어서 해당 메모리를 사용하여 합성한 것이고, 질문주신 코드의 경우는 메모리의 형태는 아니고 커스텀된 코드이기 때문에 단지 그에 맞춰서 합성이 MUX로 된 것입니다.

또 진행하시면서 궁금한 점 있다면 질문 주세요!