인프런 커뮤니티 질문&답변

ILA 관련 질문

작성

·

96

1

안녕하세요 맛비님.

날이 부쩍 더워졌네요. 더위 조심하시기 바랍니다.

LAB8 ILA 실습을 복습하는 중 warning이 떠서 질문드립니다.

실습과정 처럼 CLK을 100MHz로 인가하면 잘 되지만, CLK을 2MHz로 줄였더니 다음과 같은 warning이 뜨더라고요.

[Labtools 27-3413] Dropping logic core with cellname... at location...

[Labtools 27-1974 ] Mismatch between the design programmed and the probes

구글링 해보니 아마 timing viloation으로 인한 것 같습니다. 이것을 해결할 수 있는 방법이 있을까요?

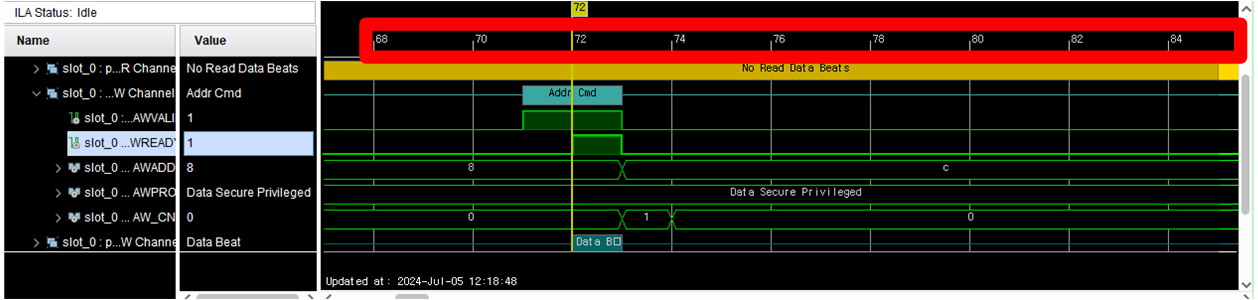

추가적으로 ILA 실습 WAVEFORM에서 x축은 sample을 뜻해보이는데, 인가한 clock의 cycle이라고 보면 될까요? 예로들어 100MHz로 인가했으면 아래의 단위 간격은 10ns일까요?

감사합니다.

답변 1

0

설계독학맛비

지식공유자

안녕하세요 🙂

A1. 2MHz 로 해본적은 없어서, 처음보는 에러이긴 하네요.

에러 메세지가, 2MHz 를 사용해서 라기보다는, 사용방법에 문제가 있으신 것 같아보여요.

ILA 연결과정에 문제가 있었지 않았을까 예상해봅니다. (timing viloation 과 연관된 에러메세지.. 와는 거리가 있어보이네요)

ILA 연결과정에 문제가 있었지 않았을까 예상해봅니다. (timing viloation 과 연관된 에러메세지.. 와는 거리가 있어보이네요)

====

A2. "100MHz 의 1 cycle 이면 10ns" 네 정확하게 맞습니다.

즐공하세요 🙂