인프런 커뮤니티 질문&답변

8강 AXI4-Lite 수강 중 입니다. Launch Hardware 진행시 작동이 안됩니다 ㅠ

작성

·

297

1

안녕하세요 맛비님.

FPGA 8장 실습을 진행하고 있습니다.

환경은 아래와 같습니다.

보드: ZYBO Z7-20

VIVADO: 2024.01

VITIS: Classic 2024.01

2022.01 이후 버젼 main.c 코드를 적용하여 사용했습니다.

Makefile에 Code 붙여넣기도 해서 Build 진행시 이상없구요.

Terminal 연결해서 UART 붙는 것 까지는 됐습니다만.. Launch Hardware 진행 후 UART창에서 아무 커맨드가 나오지 않는 현상이 지속됩니다..

프로젝트, 파일 명도 맛비님 강의랑 동일하게 진행했는데 이유가 뭔지 모르겠네요..

관련 증상에 대해 아시는 부분 있으면 답변 부탁드립니다.

답변 5

1

AMD 사이트에서는 Xil_Out32() 관련 에러가 보고되지 않았다고 했습니다.

아무리 봐도 Vitis 문제는 아닌 것 같아서, 혹시나 하는 마음에 Vivado에서 생성하는 IP가 문제인가 싶어서 찾아봤습니다.

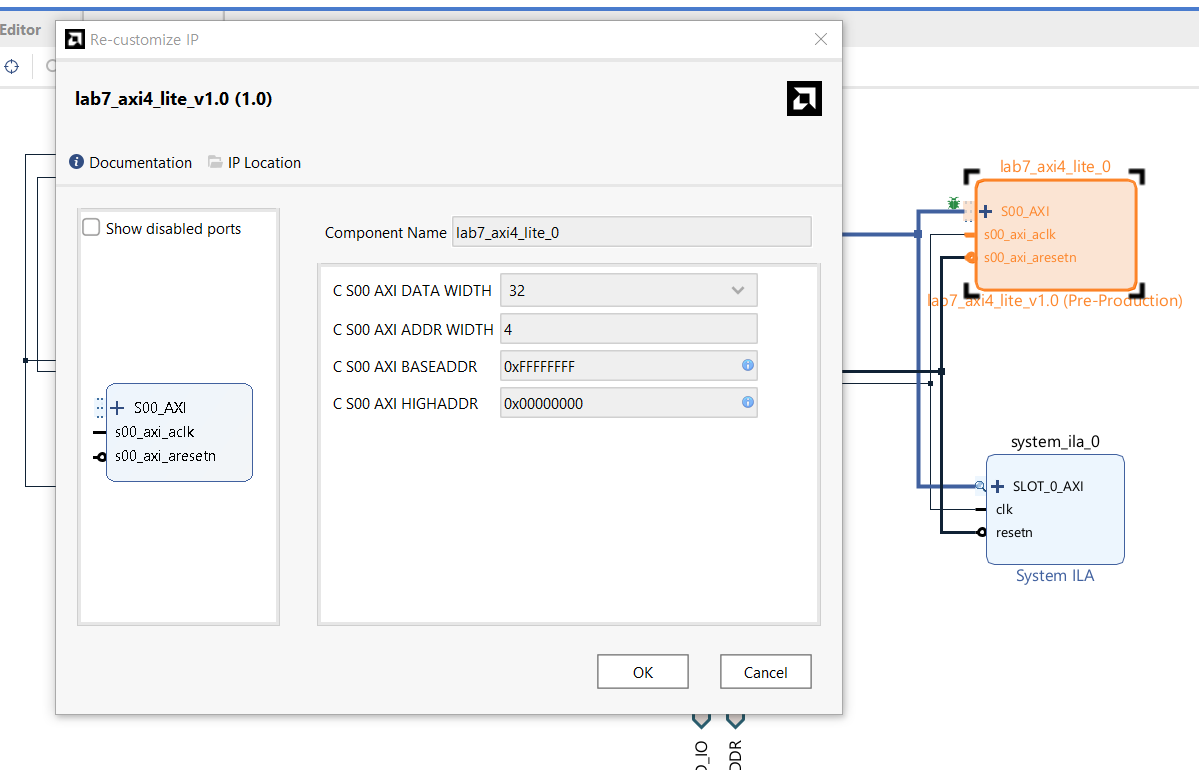

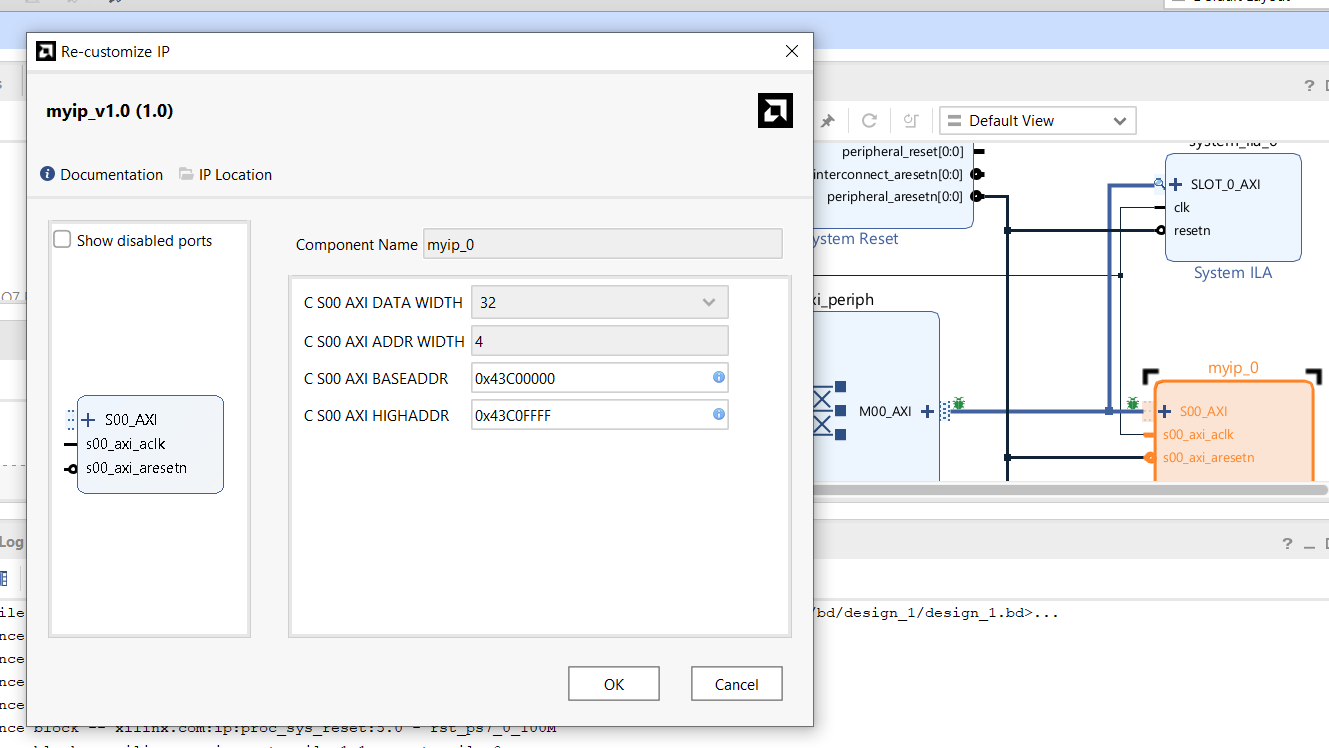

AXI4 IP 블록을 직접 확인해봤는데, 여기서 baseaddress가 이상하게 잡히는 게 문제가 되는 것 같습니다.

Address Editior에 나와있는 주소와 아예 다른 값이 나오더군요. (여기서는 0x43C0_0000 입니다.)

이 화면 상에서는 수정도 안되는 것 같고.

그냥 Vivado 2024.1 tool 버그인 것 같습니다.

+) AXI4 IP를 따로 수정해서 주소를 수정했는데도 안되네요.

이렇게 만들어도 Vitis에서 BaseAddress를 0xFFFF_FFFF로 잡아야 제대로 동작이 됩니다...

1

안녕하세요. 저도 yhd88님과 마찬가지로 8장 공부하면서 같은 문제가 발생했는데, 살펴보니 UART 문제가 아니고 Xil_Out32() 함수가 문제인 것 같네요. 쓰기 부분을 코멘트 처리하면 터미널에 데이터가 모두 0으로 출력이 되지만, 쓰기부분이 있으면 터미널에 아무것도 나타나지 않습니다. 혹시 해결방안이 있을까요?

보드: ZYBO Z7-10

VIVADO: 2024.01

VITIS: Classic 2024.01

0

오.. 다들 혼돈의 카오스 시네요.. ㅠ

버전을 강의랑 맞출 수 있다면 해결이 될 문제라고 보이는데요.

Xil_Out32() 함수의 문제까지는... 제가 해결해드리기 어려울 것 같은데,

버전을 강의와 동일하게 맞춰보는게 어떠실까 권장해드리고 싶습니다.

제가 강의에서 말하고 싶은 중요한 내용은... 아니라고 생각해요..... 빨리 다음 단계로 넘어가시기를 바랍니다.

즐공하세요 🙂

0

0

안녕하세요 🙂

8장 이전에 4장에서 UART 를 Test 하는 Lab 이 있습니다.

그 lab 은 성공하셨을까요?

build 가 성공적으로 되면 잘 되어야 할 것 같아요.

4장 성공했는데, 8장은 UART 가 안나온다 하시면..

빌드까지 하시고 Launch 까지 하셨는데 원인은 잘 모르겠네요.

버전을 맞춰주시는게 좋을 것 같습니다. 2022.1 추천드립니다.

안녕하세요 맛비님

4장 실습은 정상동작 확인하였습니다.

근데 8장 UART부분 2022.1 기준으로 진행했는데 빌드랑 Launch까지는 정상적으로 되는데 UART부분이 계속 출력이 안나오네요 ㅠㅠ

안녕하세요 맛비님

VIVADO project 및 XDC파일은 맛비님이 올려주신 파일로 진행 후 VITIS에서 프로젝트 생성 후 보드에 Writing하니까 제대로 동작하네요..ㅎㅎ

VIVADO에서 XDC 생성하는 과정에서 제대로 bit stream이 생성되지 않은것인지... 의문스럽지만 실행은 잘 됩니다! 감사합니다 ㅎㅎ

답변 감사합니다!

음... 해결방법이 좀.. 의아하긴 하네요..

BASE ADDR 라는 개념이, 시스템 상에 할당받은 address 인데,

Vivado 에서 System 구성시, Address value 와 같은 값이 셋팅되어야 할 것 같아서요.

vitis 에서 넘어오면서 이 부분을 자동으로 생성해 주었었고요.

된다고 하시기도 하고, 제가 모든 버전을 test 하기도 어려워서 ㅠ

혹시나 이글을 보시는 분들이 있다면, myflute 님의 해결방법에 참고 부탁드립니다.

감사합니다!!