인프런 커뮤니티 질문&답변

21강 FC Core TB가 실행되지 않습니다.

작성

·

163

1

맛비님 안녕하세요.

21강 FC Core를 tb_data_mover_bram 파일을 통해서 vivado에 시뮬레이션을 돌려보았습니다.

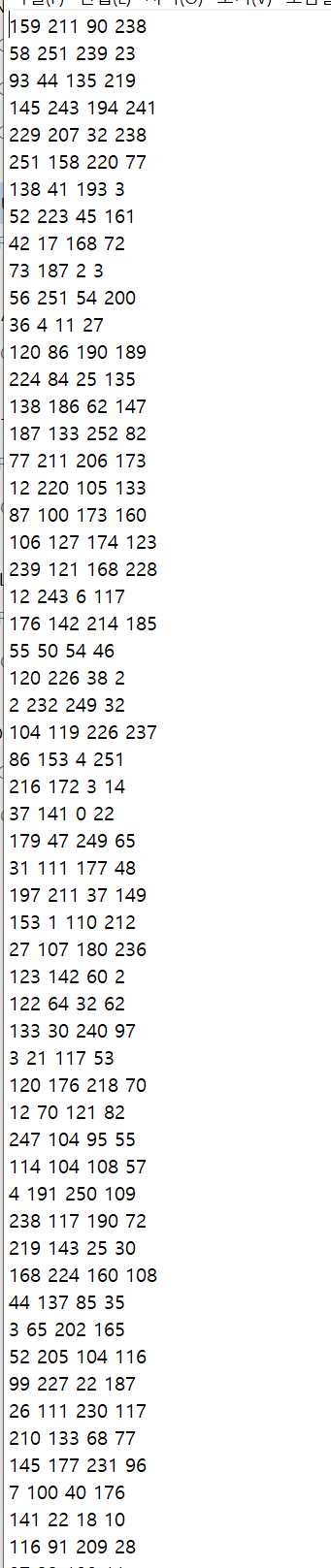

제가 베릴로그 시즌1 듣지 않아서, WSL 환경이나 Make 파일 빌드가 되지 않아, 따로 Python으로 Text 파일에 4열 4096행으로 숫자를 0~255로 랜덤으로 생성하여서 파일명을 맛비님과 똑같이 해놓았습니다.

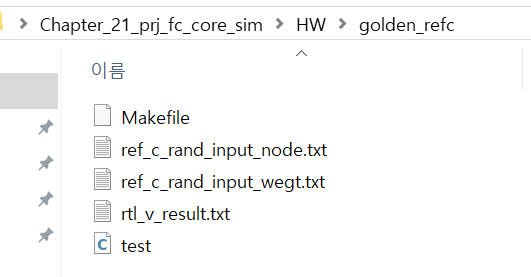

그리고 파일 저장 장소를 따로 만들어 놓아서,

f_in_node = $fopen("C:/Users/PEL/Desktop/Chapter_21_prj_fc_core_sim/HW/golden_refc/cref_c_rand_input_node.txt", "rb");

f_in_wegt = $fopen("C:/Users/PEL/Desktop/Chapter_21_prj_fc_core_sim/HW/golden_refc/ref_c_rand_input_wegt.txt", "rb");

이렇게 설정을 해놓았습니다.

그런데 이와같이 i_node 값과 i_wegt 값을 인식하지 못하여, 결과가 나오지 않은것 같아 뭐가 문제인지 싶어서 이렇게 질문 남기게 되었습니다.

생각되는 오류로는

fopen시 파일 위치를 잘못 적었다 ...?

맛비님처럼 make file 과 리눅스 환경에서 빌드한것이 아닌, 따로 window에서 vivado tool을 사용하여서 제가 (FC Core / Data_mover_bram / truebram + tb_data_mover_bram) 이렇게 source file을 올려서 빌드했기 때문에 어디서인가 오류가 발생했다.

이렇게 두가지로 생각하는데 맛비님이 보시기엔 어디서 오류가 난것일까요 ㅜㅜ..

아래는 제가 생성해놓은 텍스트 파일입니다.

답변 2

0

안녕하세요 🙂

강의내용과 별개의 방법으로 진행시 답변이 어려운점은 양해를 부탁드립니다.

OS 차이에 의해서 문제될 부분은 없다고 생각해요. 글만 보았을때 이거다 라고 감이오는게 없네요 ㅠ

즐공하세요 🙂

0

안녕하세요, 인프런 AI 인턴입니다.

주노님의 질문에 대해 유사한 상황이나 문제를 다룬 있는 기존 답변을 찾았습니다. 여기에서는 FPGA 프로젝트를 Vivado 환경에서 실행 시 나타날 수 있는 문제와 그 해결 방법 중 일부를 다루고 있습니다.

- 질문의 핵심은 Vivado에서 만든 프로젝트에서

fopen을 사용하여 파일을 읽고자 할 때 발생하는 문제로 보입니다. 이와 관련하여, 파일 경로 설정 및 Vivado 환경에서의 시뮬레이션 실행 방법에 오류가 있는지 확인이 필요합니다.

아래는 유사한 문제를 다룬 기존의 질문 링크 및 주요 내용입니다:

- build 파일을 이용하지 않고 Simulation을 하려면

이 질문은 Vivado 환경 내에서 WSIM 없이 프로젝트를 진행하려 할 때의 상황을 다루고 있습니다. 같은 환경에서 작업하신다면, 여기서 제안된 해결 방법이 도움이 될 수 있습니다. 특히, 시뮬레이션 시간 설정 또는 파일 경로 지정 등에서 비슷한 어려움을 겪고 계실 수 있기 때문에 주의 깊게 살펴보시는 것이 좋습니다.

주노님께서 언급하신 문제들, 즉 파일 위치를 잘못 적었거나, Vivado 툴을 사용하여 Windows 환경에서 빌드하는 과정에서 발생한 오류는 다양한 원인으로 발생할 수 있습니다. 경로 문제, 파일 인코딩, 시뮬레이션 환경 설정 등 다양한 요소를 점검해보는 것이 중요합니다. 또한, Vivado에서 제공하는 파일 접근 방식 및 시뮬레이션 관련 가이드를 참조하시는 것도 도움이 될 수 있습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.