인프런 커뮤니티 질문&답변

9장 generate문 질문

작성

·

686

1

안녕하세요 맛비님

강의에 generate문에 대해 배우며 궁금한 점이 생겼습니다

verilog에 generate for~ 문이 아닌 그냥 for문도 존재하고, 이를 통해 하드웨어가 합성된다고 알고 있는데요

generate for~ 문과 그냥 for ~문을 사용했을 때 합성되는 하드웨어의 차이가 궁금합니다.

=================

현업자인지라 업무때문에 답변이 늦을 수 있습니다. (길어도 만 3일 안에는 꼭 답변드리려고 노력중입니다 ㅠㅠ)

강의에서 다룬 내용들의 질문들을 부탁드립니다!! (설치과정, 강의내용을 듣고 이해가 안되었던 부분들, 강의의 오류 등등)

이런 질문은 부담스러워요.. (답변거부해도 양해 부탁드려요)

개인 과제, 강의에서 다루지 않은 내용들의 궁금증 해소, 영상과 다른 접근방법 후 디버깅 요청, 고민 상담 등..

글쓰기 에티튜드를 지켜주세요 (저 포함, 다른 수강생 분들이 함께보는 공간입니다.)

서로 예의를 지키며 존중하는 문화를 만들어가요.

질문글을 보고 내용을 이해할 수 있도록 남겨주시면 답변에 큰 도움이 될 것 같아요. (상세히 작성하면 더 좋아요! )

먼저 유사한 질문이 있었는지 검색해보세요.

잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

==================

답변 1

0

안녕하세요 🙂

Verilog 문법 질문이신 것 같은데요.

GPT4 를 통해서 답변드리겠습니다. (문법 내용 기술은 GPT 가 잘합니다. 제 생각도 같아요.)

=========== GPT =============

Verilog에서 generate for문과 그냥 for문은 비슷해 보일 수 있지만, 사용 목적과 합성되는 하드웨어에 있어서 중요한 차이점이 있습니다.

차이점

사용 시점:

generate for는 elaboration 시간에 사용되어 실제 하드웨어 구조를 생성하는 반면, 일반for문은 시뮬레이션 또는 동작 시간에 평가되어 로직을 구현합니다.합성 결과:

generate for를 사용하면 독립적인 여러 하드웨어 인스턴스가 생성되는 반면, 일반for문을 사용하면 단일 로직 블록 내에서 반복 연산이 수행됩니다.사용 목적:

generate for는 구조적 반복을 위해, 일반for문은 동작적 반복을 위해 사용됩니다.

=========== GPT end =============

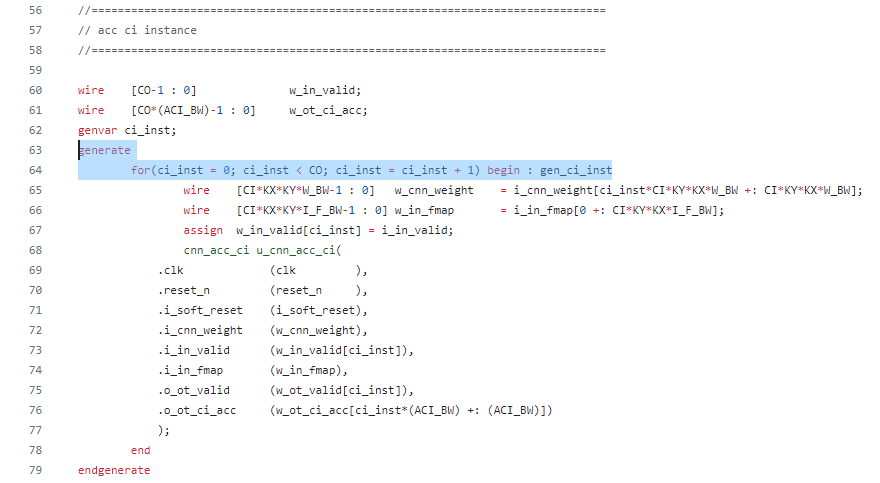

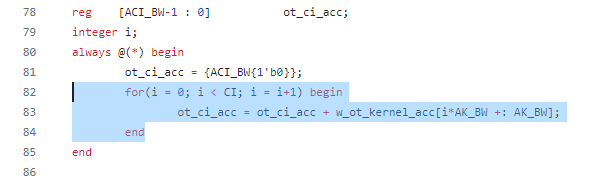

따라서, 전달드린 코드를 보시면, instance 를 여러개 생성할때 generate for 문을 사용했고요.

for 문은 로직의 동작을 기술할 때 사용하였습니다.

즐공하세요 🙂

안녕하세요, 질문을 정확하게 이해하지 못했는데요.

"같게 밖에 못만드나요?" 의 예가 어떤 걸까요??

생각하시는 코드가 있으시면 수정해보시고 build 돌려보시는 것도 답에 도움이 되실 것 같아요.

generate로 instance할 때, instance name은 같게 밖에 못만드나요??