인프런 커뮤니티 질문&답변

[20장] direct assign 관련 질문

작성

·

203

·

수정됨

1

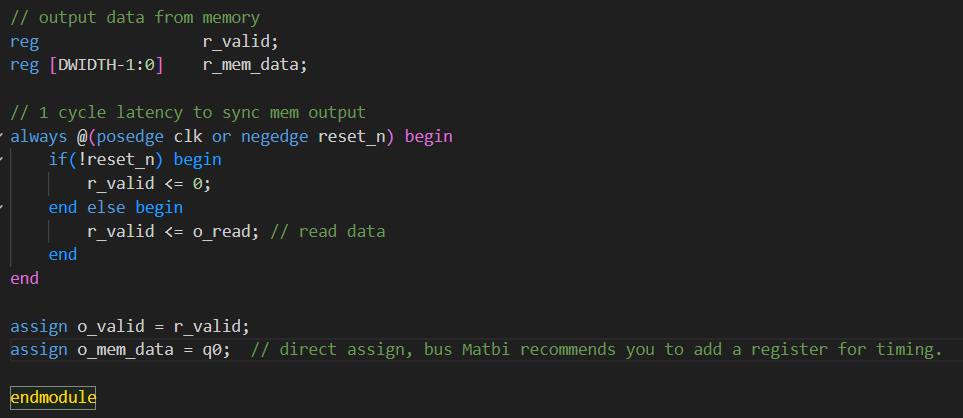

simple_bram_ctrl 모듈에서 bram으로 부터 받은 입력(q0)을 바로 o_mem_data에 assign 한 것에 대해 레지스터를 통해 연결하는 것을 추천한다고 주석을 달아주셔서

simple_bram_ctrl 모듈에서 bram으로 부터 받은 입력(q0)을 바로 o_mem_data에 assign 한 것에 대해 레지스터를 통해 연결하는 것을 추천한다고 주석을 달아주셔서

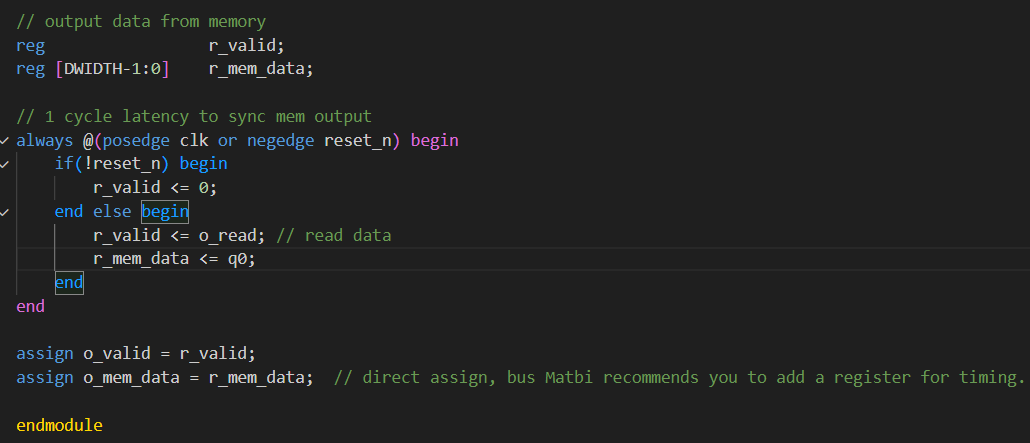

이런 식으로 레지스터를 통해 연결을 하면, 예상한 것과 같이 bram에서 이미 1 clk 뒤에 출력하기 때문에 결과적으로 2 cycle 후에 데이터가 출력이 되는 상황이 발생하였습니다.

이런 식으로 레지스터를 통해 연결을 하면, 예상한 것과 같이 bram에서 이미 1 clk 뒤에 출력하기 때문에 결과적으로 2 cycle 후에 데이터가 출력이 되는 상황이 발생하였습니다.

맛비님께서 말씀하신 것처럼 레지스터를 활용하여 출력을 하는데 실습 결과처럼 1cycle 뒤에 데이터가 출력되게 하기 위해서는 어떤 식으로 코드를 구성해야하는지 조언해주시면 감사하겠습니다.

추가로 r_mem_data를 선언하시고 실제로 실습에서 사용 안하신 이유가 궁금합니다.

답변 1

0

설계독학맛비

지식공유자

안녕하세요 🙂

A1.

F/F 을 사용하면 당연히 1 cycle 이 밀리는 것이 맞습니다.

잠깐 보았을때, 현재 수정하신 코드에서 r_valid 도 1 cycle 같이 미뤄주시면 sync 를 맞출 수 있을 것 같네요.

질문자님께서 직접 수정하신 강의 코드의 동작은 저도 보장을 해드리기 어렵습니다. 당연히 설계자가 책임져야겠죠?

A2.

이유는 강의의 설명을 위함이다 말씀드리고 싶어요. 큰 이유는 없습니다. (timing 이슈가 없다면 지금 제가 드렸던 기존 코드로도 충분합니다.)

1 cycle 이 delay 되어도 문제없다고 설계자(질문자님)가 인정하면, 수정하신 것처럼 사용하시면 됩니다.

즐공하세요 🙂