인프런 커뮤니티 질문&답변

counter 질문

작성

·

163

1

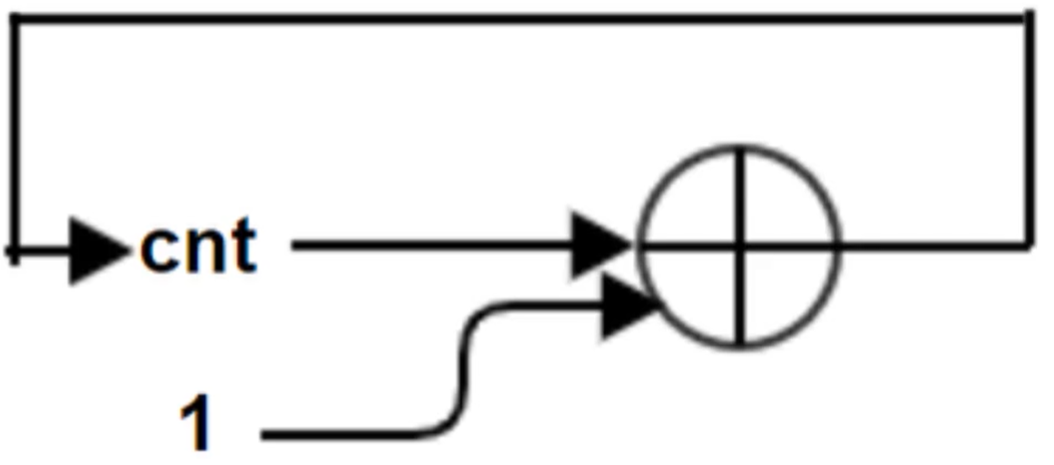

counter 이론편에서 말씀하시길

cnt = cnt +1이라고 verilog로 기술하면 안된다고 말씀하셨는데

(이러면 전기 신호가 한 바퀴 도는 거라고 말씀하셨습니다!) 이 부분이 잘 이해가 되지 않네요

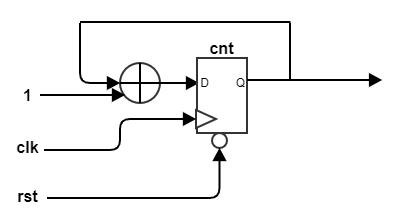

시퀀셜 로직을 설계할 땐 nonblocking을 쓰는 것이 국룰이라고 배우긴 했습니다만

if 문 안에서

cnt = cnt +1 한 문장 뿐이니 밖에 없으니까 blocking을 쓰던 nonblocking을 쓰던

오른쪽 cnt 를 왼쪽 cnt에 할당하기 위해선 이전 clk에서 결정된 cnt 값이 할당돼야 하므로

여튼간에 f/f가 만들어지니 상관없는 거 아닌가요??

답변 1

0

설계독학맛비

지식공유자

안녕하세요 🙂

다음 코드의 차이와 생성되는 회로를 생각해 보시면 답이 되실 같아요.

Case 1. combination logic =================================

wire [7:0] cnt ;

assign cnt = cnt + 1; // (불가능)

Case 2. sequential logic ==================================

reg [7:0] cnt;

always @ (posedge clk) // reset 생략

cnt <= cnt + 1; // (가능)

즐공하세요 🙂