인프런 커뮤니티 질문&답변

40page project build 관련하여 error가 있는데 해결을 못하고 있습니다.

작성

·

437

0

강의안 40page 관련하여 질문이 있습니다.

강의안 40page 관련하여 질문이 있습니다.

40page project build 관련하여 error가 있는데 해결을 못하고 있습니다.

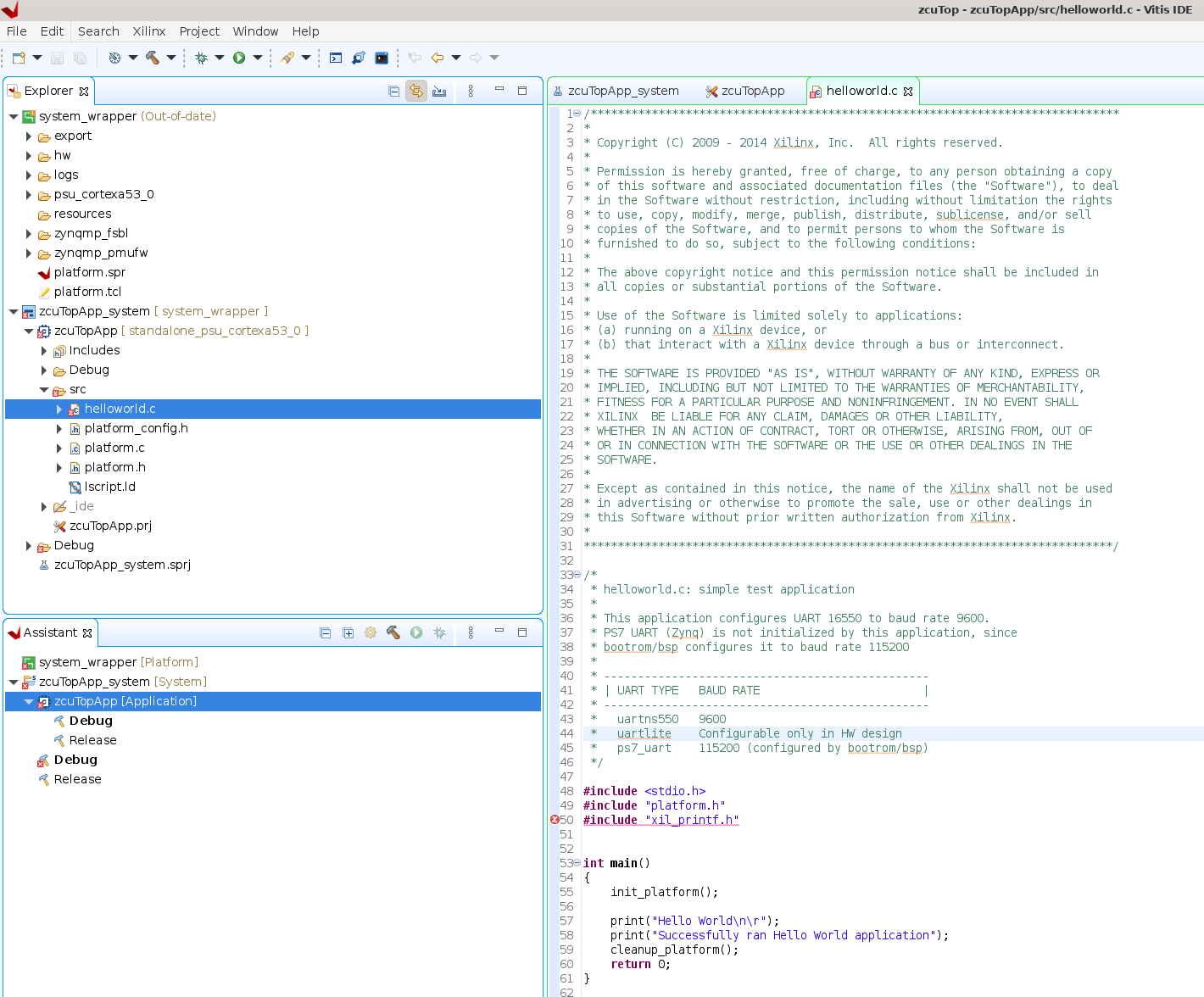

xsa 파일 불러와서 Hello World 예제 그대로 생성하였는데 저는

#include "xil_printf.h"

가 제대로 링크되어 있지 않습니다.

어떻게 해결해줘야할 지 모르겠습니다..

15:19:55 **** Build of configuration Debug for project zcu_1226_App2 ****

make all

Building file: ../src/helloworld.c

Invoking: ARM v8 32 Bit gcc compiler

arm-none-eabi-gcc -Wall -O0 -g3 -c -fmessage-length=0 -MT"src/helloworld.o" -march=armv7-a -mfpu=vfpv3 -mfloat-abi=hard -I/home/jhsong/Desktop/zcu_1226/system_wrapper/export/system_wrapper/sw/system_wrapper/standalone_psu_cortexa53_0/bspinclude/include -MMD -MP -MF"src/helloworld.d" -MT"src/helloworld.o" -o "src/helloworld.o" "../src/helloworld.c"

../src/helloworld.c:50:10: fatal error: xil_printf.h: No such file or directory

50 | #include "xil_printf.h"

| ^~~~~~~~~~~~~~

compilation terminated.

make: *** [src/subdir.mk:26: src/helloworld.o] Error 1

15:19:56 Build Finished (took 660ms)

분명 xil_printf.h 헤더파일은 프로젝트 파일 내부 폴더 안에 여러개 생성되어있는 것도 확인했습니다.

./system_wrapper/psu_cortexa53_0/standalone_psu_cortexa53_0/bsp/psu_cortexa53_0/libsrc/standalone_v7_3/src/common/xil_printf.h

./system_wrapper/psu_cortexa53_0/standalone_psu_cortexa53_0/bsp/psu_cortexa53_0/libsrc/standalone_v7_3/src/xil_printf.h

./system_wrapper/psu_cortexa53_0/standalone_psu_cortexa53_0/bsp/psu_cortexa53_0/include/xil_printf.h

./system_wrapper/zynqmp_fsbl/zynqmp_fsbl_bsp/psu_cortexa53_0/libsrc/standalone_v7_3/src/common/xil_printf.h

./system_wrapper/zynqmp_fsbl/zynqmp_fsbl_bsp/psu_cortexa53_0/libsrc/standalone_v7_3/src/xil_printf.h

./system_wrapper/zynqmp_fsbl/zynqmp_fsbl_bsp/psu_cortexa53_0/include/xil_printf.h

답변 2

0

zcu_1226_App 으로 했을 때 되지 않아 다시zcu_1226_App2_system 으로 시도하였습니다.

새로 vivado부터 프로젝트 수회 새로 만들어 시도를 해도 전부 똑같은 문제가 발생하였습니다.

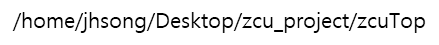

1. vivado 2020.2 실행

zcuTop 프로젝트 생성

RTL Project 체크

zcu104 보드 선택

프로젝트 생성

design block name : system

IP추가 : zynq Ultrascale + MPSOC

PS-PL 영역 체크 해제, uart0과 qspi만 체크

Run Bloack Automation

Validate Design success 확인

Generate Output Product 후 Create HDL Wrapper

File - Export - Export Hardware

xsa file name : system_wrapper

vitis 실행하여

workspace 를 Launch

workspace 를 LaunchCreate Application Project

Create a new platform from hardware 탭에서 export 된 xsa 파일 선택

Application project name : zcuTopApp

32비트로 만들어서도 Hello world 템플릿 컴파일 시 에러가 났고, 64비트 아키텍쳐로 설정해도 결과는 바뀌지 않았습니다.

원래 해당 프로젝트에 system_wrapper 디렉토리가 생성이 안되는 건지 제꺼만 되지 않았는지도 궁금합니다.

분명 해당 경로 에 가보면 "xil_printf.h" 파일은 있는데 제대로 링크가 되지 않고 있습니다..

0

보통 프로젝트 생성시 폴더를 잘못 설정하는 경우 (vivado or vitis), 패스가 잘못 설정되어 발생하는 문제인것 같습니다. 프로젝트 이름인 zcu_1226_App, zcu_1226_App2_system 인 것으로 보아 이러한 문제인 것 같습니다. 참고로 vivado에서 프로젝트를 생성하고, vitis에서 프로젝트 생성 후, 다른 것을 진행하기 위하여 vivado 프로젝트를 그대로 사용하고, vitis에서 프로젝트를 새로 생성하거나 다른 프로젝트를 생성해서 사용하면 패스 설정이 오류를 일으킬 수 있습니다.

강의 내용대로 처음부터(vivado 부터) 다시 해 보시길 바랍니다.

감사합니다 ~!!

툴이 제대로 동작하지 않으면 어려움이 많습니다 ㅠ

아래와 같이 몇가지 방법을 시도해 보시길 바랍니다.

1) 경로에 한글이나 공백이 있으면 오류가 발생할 수 있습니다. C:, D: 에 간단한 work 폴더 생성해서 다시 진행해 보시길 바랍니다.

2) 프로젝트 생성시 zcu104보드 대신에 강의에 나와 있는 내용대로 진행해 보시길 바랍니다. Build까지만 진행해서 오류가 발생하는지 확인해 보세요.

3) 툴을 교제와 같이 "vitis 2022.1 " 버전을 설치해서 진행해 보세요. 생각보다 툴에서도 문제가 발생하는 경우가 있습니다.

조금씩 하시다 보면 툴에 익숙하게 되고, 에러가 발생해도 금방 찾게 되니 천천히 진행해 보시길 바랍니다. 감사합니다 ~!!