인프런 커뮤니티 질문&답변

17장과 20장의 FSM 부분 질문입니다.

해결된 질문

작성

·

243

·

수정됨

1

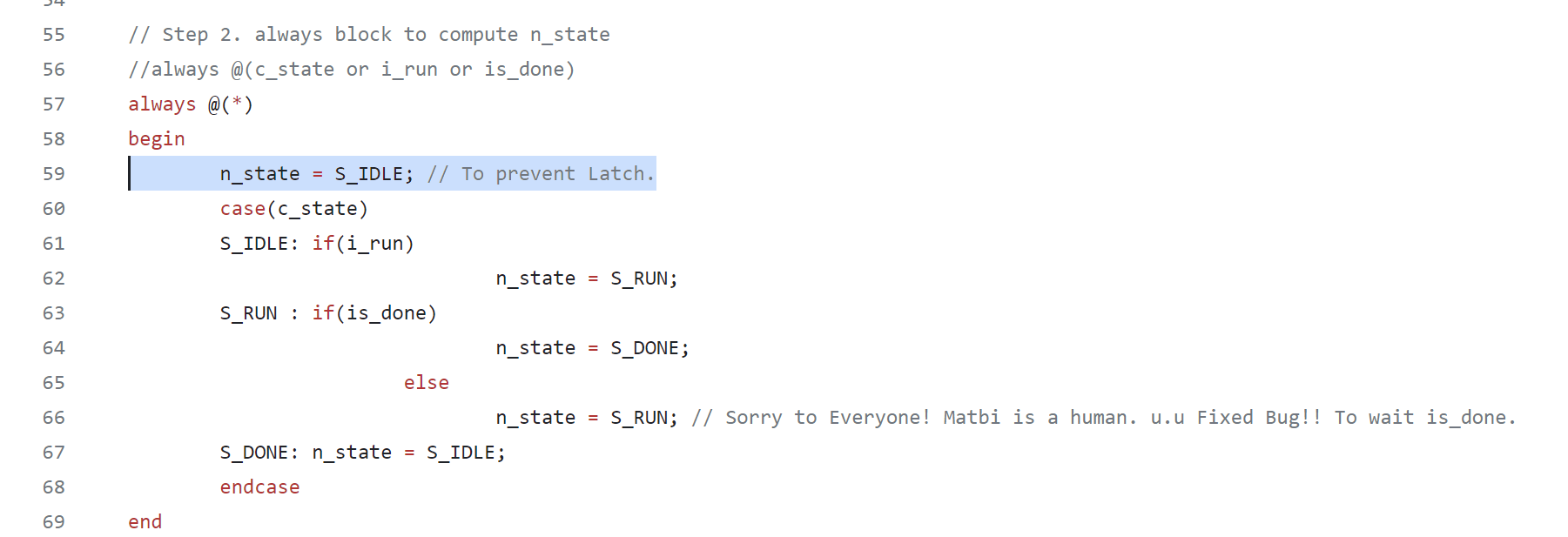

17장의 core counter 설계에서 FSM을 작성할때

S_RUN state에서 if -else 구문의 else 로 n_state = S_RUN을 넣고

그 이유로 'RUN상태를 쭉 유지하기 위해 else를 하고 현재 상태를 input으로 넣는다, 이 부분이 빠지면 100을 줘도 100 cycle 동안 run을 유지하지 않는다. 일종의 버그다' 라고 하셨는데요.

해당 부분이 잘 이해가 안가서 질문드릴 내용은 다음과 같습니다.

카운터가 동작은 하는데 중간에 카운터가 오동작을 한다는 뜻인가요 ?(즉 카운팅을 하다가 중간에 카운팅이 되지 않는다는 뜻인지?)

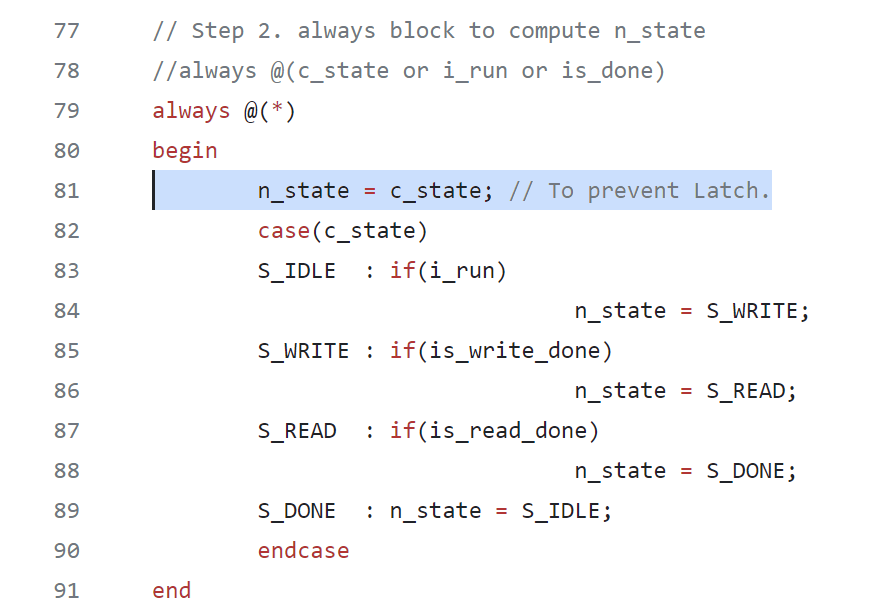

17장의 else를 위와 같은 이유(버그 방지)로 추가 하였다면, 왜 20장 BRAM Cotnroller FSM의 read/write state 에서는 else 구문을 사용하여 counter의 run 동작 버그 방지를 하지 않는지 궁금합니다. 같은 이유로 버그가 생길 수 있는거 아닌가요 ??

답변 1

1

안녕하세요 🙂

1번하고 2번이 상충되는데요.

17장의 가장 큰 문제는 59번째 라인이었습니다. n_state 를 S_IDLE 로 가져갔기 때문이에요.

사실 65, 66번째 라인 부분을 빼고, 59번째 라인을 n_state = c_state; 로 바꿔도 동작합니다.

이 부분을 17장에서는 65, 66번째 라인처럼 수정해도 됩니다. (동작은 정상적으로 하니까 뭐가 맞냐 틀리냐는 아닌 것 같아요.)

20장코드는 81번째 라인에 제대로 들어가 있습니다.

이야기의 결론은 17장 20장 전부 동작에는 문제 없고요.

하지만!! 제가 추천드리는 방법은 20장 방법을 추천드립니다.

n_state = c_state;

즐공하세요 :)

감사합니다~!