인프런 커뮤니티 질문&답변

AXI4 버스 점유와 관련된 질문이 있습니다!

작성

·

288

1

=================

현업자인지라 업무때문에 답변이 늦을 수 있습니다. (길어도 만 3일 안에는 꼭 답변드리려고 노력중입니다 ㅠㅠ)

강의에서 다룬 내용들의 질문들을 부탁드립니다!! (설치과정, 강의내용을 듣고 이해가 안되었던 부분들, 강의의 오류 등등)

이런 질문은 부담스러워요.. (답변거부해도 양해 부탁드려요)

개인 과제, 강의에서 다루지 않은 내용들의 궁금증 해소, 영상과 다른 접근방법 후 디버깅 요청, 고민 상담 등..

글쓰기 에티튜드를 지켜주세요 (저 포함, 다른 수강생 분들이 함께보는 공간입니다.)

서로 예의를 지키며 존중하는 문화를 만들어가요.

질문글을 보고 내용을 이해할 수 있도록 남겨주시면 답변에 큰 도움이 될 것 같아요. (상세히 작성하면 더 좋아요! )

먼저 유사한 질문이 있었는지 검색해보세요.

잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

==================

안녕하세요 맛비님 늘 많이 배우고 있습니다.

날이 급격하게 추워졌는데 감기 조심하시길 바랍니다 😃

다름이 아니라 이렇게 질문글을 남기게 된 건 버스 점유와 관련된 질문이 있어서인데요.

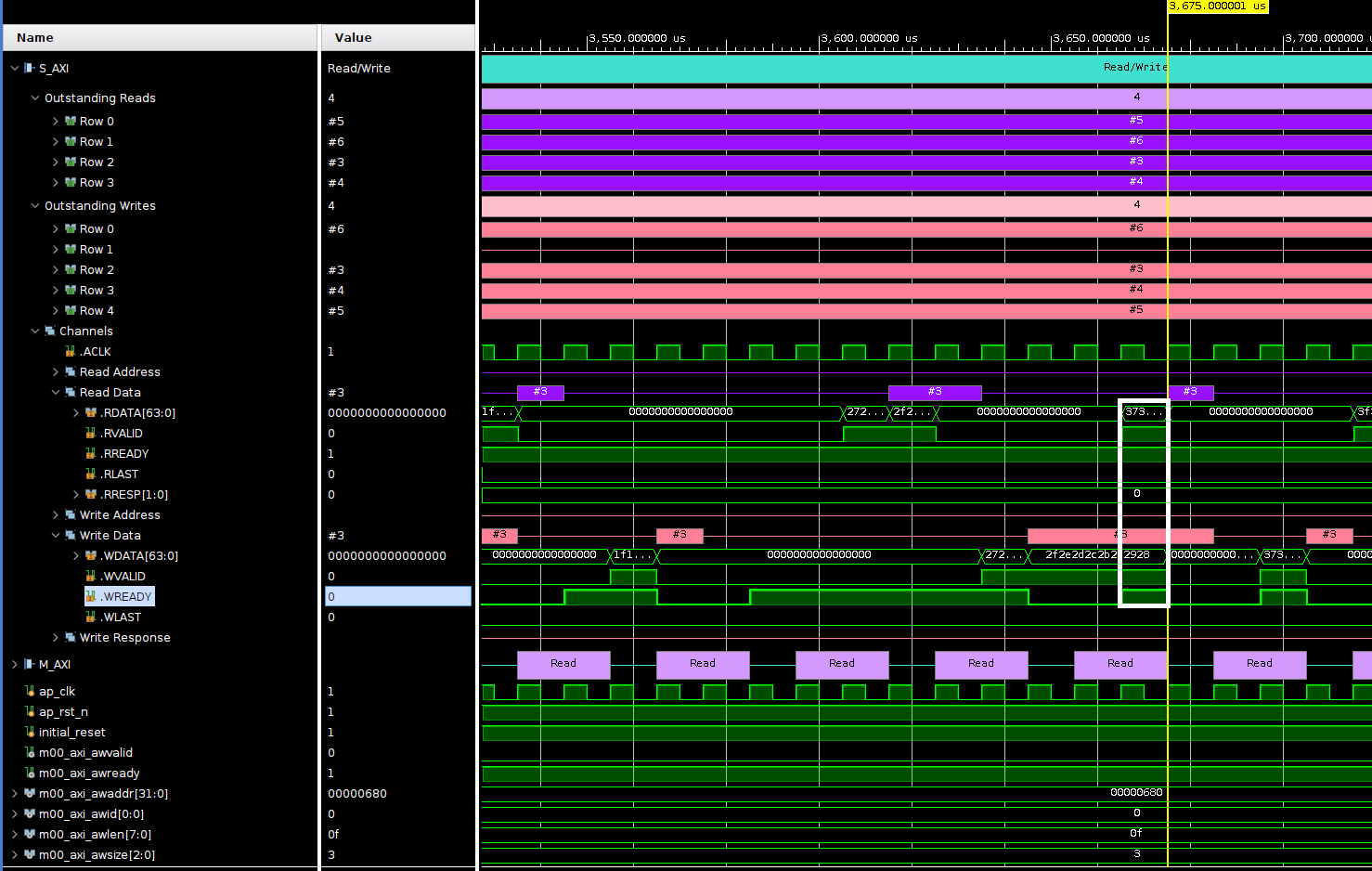

아래 사진이 잘 보이실 지 모르겠는데, 하얀색 네모 박스로 쳐져있는 부분에서 READ, WRITE transaction이 일어난 것 같은데 이러면 버스 width를 64bit로 설정해둔 지금(chapter20) 버스의 점유 원칙(이런 말이 있나모르겠네요)? 이런 거에 위배되지 않나요? 강의에서 놓친 부분이 있다면 미리 죄송하다는 말씀 드립니다..ㅠ

그럼 답변 기다리겠습니다. 감사합니다.

답변 1

0

안녕하세요 🙂

AXI 에서 Read 와 Write Transaction 이 동시에 일어나는 것은 스펙 상 아무 문제가 없습니다. (그렇게 되어야 performance 이득이 있습니다.)

왜냐하면 Read Channel 와 Write Channel 은 서로 독립적으로 존재하며, Bus 관점에서는 동시 처리가 가능합니다. 다만 Read 와 Write 의 목적지 (ex DDR) 가 동일하다면, DDR 내에서 Read 를 먼저 할지 Write 를 먼저 할지는 갖고있는 rule 에 의해서 우선순위를 정하겠죠.

이때 우려되는 사항은

같은 Read Channel 와 Write Channel Address 를 접근했을때, 이때가 가장 문제이고요.

처리를 어떻게 해줄 것인가는 Architecture 의 역할이라고 봐요.

보통 어떻게 하냐면, 동작중에 Read 와 Write 가 Address 가 겹치지 않게 설계를 합니다.

아키텍쳐 관점에서 예를 들면 Read 영역과 Write 영역을 분리하고, 서로 ping pong 으로 swithcing 하면서 동작하도록 제어.

결론은 AXI 에서 Read 와 Write 동시 Transaction 은 스펙 위반이 아니다.

같은 Address 를 접근했을때, 어떻게 처리하느냐에 따라서 결과가 달라진다.

이 결과는 설계자가 의도한대로 동작하도록 정해줘야한다. 입니다.

즐공하세요 :)