인프런 커뮤니티 질문&답변

Timig관련 질문있습니다.

작성

·

454

·

수정됨

2

*댓글 먼저봐주시면 감사하겠습니다! 댓글 내용이 이해된다면 게시글 질문도 이해가 될 것 같습니다!

<Data mover BRAM 220번째 라인>

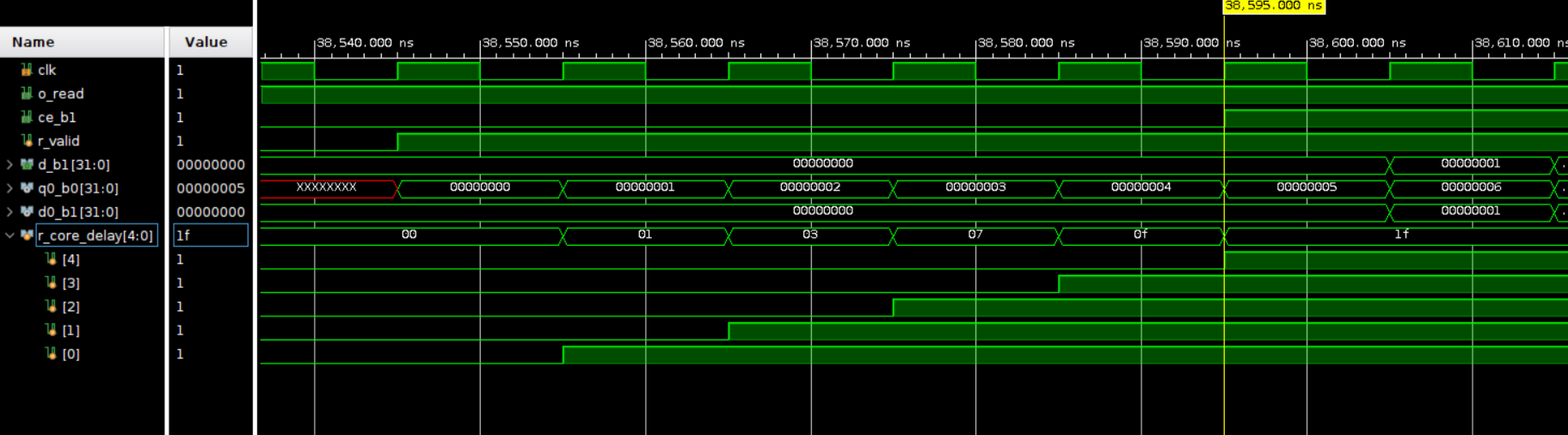

assign we_b1 = r_core_delay[CORE_DELAY-1];여기서 we_b1이 켜지고 (r_core_delay == 1f)

한 사이클 후에

<DPBRAM 55번째 라인>

always @(posedge clk)

begin

if (ce0) begin

if (we0)

ram[addr0] <= d0;

else

q0 <= ram[addr0];

end

endBRAM1에 0이 write돼야되는거아닌가요?

어떻게 we_b1이 켜짐과 동시에 write되는지 이해가 잘 가지 않습니다ㅠㅠㅠ 기본기가 부족해서 그런걸까요..

답변 4

1

1

추가로 d0_b1에 (r_core_data[0]에 addr 0번지는 뛰어넘고 1번지 data부터 저장되기 때문에) 1번지 data(1)부터 write하는걸로 이해했는데 맞나요?

추가로 제가 이해한 flow는 다음과 같습니다.

추가로 제가 이해한 flow는 다음과 같습니다.

(화살표는 다음사이클로 넘어감을 의미)

r_valid = 1

-> r_core_delay = 00001 ( r_core_data block 조건 충족 (시작) )

-> r_core_data[0] = mem_data[1번지]

(0번지에는 reset data write)

0

0

우선 코드 이해도가 높지못해 질문을 모호하게 드린거같아 죄송합니다. 제가 write, read 동작 구분을 제대로 못해 질문에 혼선이 생겼던거같습니다. 다음과 같은 이유로 16장에서 코드를 수정하신게 맞으신지 궁금합니다!

// first one

always @(posedge clk or negedge reset_n) begin

if(!reset_n) begin

r_core_data[0] <= {DWIDTH{1'b0}};

end else if(|r_core_delay) begin

r_core_data[0] <= mem_data; //(2번 조건)

end

endr_core_delay 신호가 들어가면 2번조건이 실행돼 BRAM0번에 값을 read해 r_core_data에 저장 후 5사이클 delay된 후 그 값이 BRAM1에 write됩니다.

근데 읽어오는 과정(위에 코드)에서 저렇게 |r_core_delay 조건이 붙게되면 시작시 BRAM0 0번지가 아닌 1번지에 값을 읽어오며 시작됩니다.(write 0 시점에는 BRAM 0번지에 reset값이 들어감(ex. reset값이 5엿다면 5, 1, 2, 3 ... 순으로 write된다.)

안녕하세요 :)

추가로 d0_b1에 (r_core_data[0]에 addr 0번지는 뛰어넘고 1번지 data부터 저장되기 때문에) 1번지 data(1)부터 write하는걸로 이해했는데 맞나요?

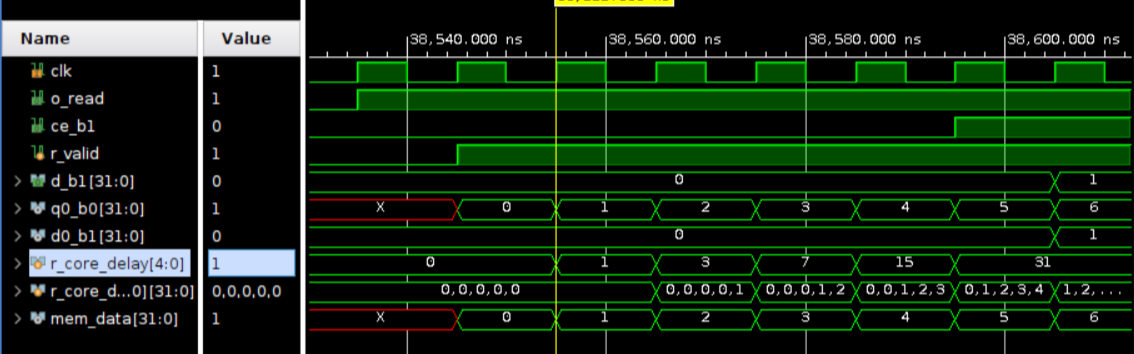

아닙니다. 0 번지부터 1씩 증가하면서 write 합니다. 즉, 1 번지 부터 write 하는 것이 아닙니다.

위 코드를 보시면,

addr_cnt_write 의 초기 값은 0입니다.

그리고, 157 번째 line 의 o_write && we_b1 일때 counting 이 증가하죠.

0 -> 1 -> 2 -> ...

write 0 시점에, we_b1 까지 같이 확인해보시면 될 것 같아요.

다음 waveform 의 노란색 signal 부분 및 timing 참고 부탁드려요.